# Reusable SOLS Encoder for DSRC Applications

Arya Krishnan<sup>1</sup>, Anusree L. S.<sup>2</sup>

<sup>1</sup>P G Scholar, VLSI and Embedded Systems, Department of ECE, T K M Institute of Technology, Kollam, India

<sup>2</sup>Assistant Professor, Department of ECE, T K M Institute of Technology, Kollam, India

Abstract: The dedicated short range communication (DSRC) is a protocol mainly used for intelligent transportation system. The information signals transmitted by this protocol are encoded by using either FM0 or Manchester codes. The code diversity between these two codes limits the designing of a VLSI architecture that supports the both. Hence this paper put forward a new VLSI architecture design which can be fully reused by using both the codes. This design based on similarity oriented logic simplification (SOLS) technique achieves an efficient performance compared with sophisticated works. This design flow can be attained in VHDL language by using Xilinx development board.

Keywords: SOLS, FM0 encoding, Manchester encoding, DSRC protocol, CRC.

#### 1. Introduction

Dedicated Short Range Communication (DSRC) is a protocol used for communication for a short range of distance, say a few hundred meters through a dedicated channel. It is used to introduce intelligent transport system into our day to day life. The DSRC communication aids in both vehicle to vehicle communication as well as vehicle to roadside communication. The vehicle to vehicle communication mainly deals with the collision alarms, hard break warnings etc. At the same time the vehicle to infrastructure communication includes the Electronic Toll Collection (ETC), highway-rail intersection warning, in vehicle signing etc. However the primary motivation of the DSRC communication channel is collision detection and vehicular safety. In addition to it, it also aids in smooth traffic control.

The DSRC equipment mainly consists of three modules namely; base band processors, RF front end and the microprocessors. The microprocessors are responsible for scheduling the tasks of base band processing and RF front end and intercept the instructions. The RF front end takes care of the transmission and reception of data. Finally main function of the base band processing includes modulation, error correction, clock synchronization, and encoding. For the purpose of encoding data, normally an FM0 or Manchester encoding are used so as to reduce the chances of occurrence of noise in the channel when it is left idle.

When a system that can be reused between both the FM0 and the Manchester encoding is implemented, the hardware utilization rate is reduced thereby reducing the efficiency. This in turn affects the performance of the system. Hence a new method of designing a reusable VLSI architecture is proposed. This novel method of designing called the Similarity Oriented Logic Simplification (SOLS) improves the hardware utilization rate of the reusable architecture thereby improving the performance and area footage.

#### 2. Related Technologies

#### 2.1 DSRC Protocol

Dedicated short range communication (DSRC) is a fast, short to mid range, wireless technology. It enables one way or two way communication between vehicles or between vehicles and roadside. It is to used make streets safer, travel easier and minimizes the impact vehicles have on the environment. It provides vehicles and infrastructure the ability to communicate with each other at a rate of 10 times per second. [1]

In DSRC communication, the most important concern is collision detection. Each DSRC equipped vehicle broadcasts its basic information including speed, trajectory, location etc to a short range of distance, say a few hundred meters. All other DSRC equipped vehicles in the vicinity receives this message. Later on this message is decoded by the receiver vehicles and a caution or warning may be issued to the driver. This can be issued audibly, visually or haptically [3].

The DSRC communication is based on direct communication between vehicles and hence does not need networking. Therefore it is also referred to as single hop. This type of communication can also be referred to as uncoordinated broadcast messaging. Each DSRC equipped vehicles can extend this network to its neighbors and hence this network can grow unbounded. In case of safety, privacy is also an important concern. Therefore all safety communications are carried out in the control channel only. The safety communication involves two types of messages:

- Routine safety messages: These are status messages including change of speed, location, etc that are regularly sent by the vehicle.

- Event safety messages: These are messages that signify an event like a hard brake.[3]

## 3. Methodology

### 3.1 FM0 Encoding

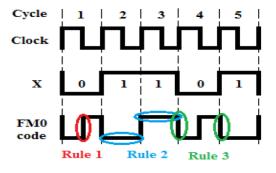

FM0 encoding is also a type of Non-Return to Zero code. It is also used to represent the binary signals in a digital system. In FM0 encoding, even though the data stream does not encounter transition, the encoded signal experiences a transition for every clock cycle. The FM0 encoding can be specified by using the three basic rules[1]. They are as follows:

1. There should be transition for every logic zero input within a clock cycle.

2. There should be no transition for logic one input.

3. There should be a transition after every clock cycle irrespective of the input data.

These rules can be better be explained by using the diagram (Fig 2).

Figure 2: FM0 encoding.

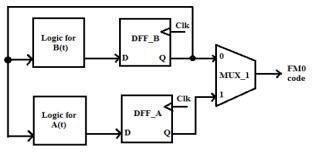

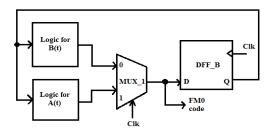

FM0 encoding can be realized by using two flip-flops and also multiplexers. The FM0 encoding can be implemented by using the block diagram as shown below in fig 3. In the following block diagram, A(t) and B(t) signifies the two states.

Figure 3: FM0 encoder

## 3.2 Manchester Encoding

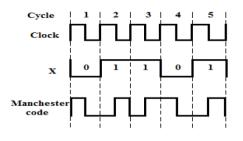

One of the most common data coding methods used today is Manchester encoding. Manchester coding gives a way of adding the data rate clock to the message to be used at the receiving end. To represent the binary values 1 and 0 in digital system, the Manchester codes are used. Manchester code represents binary values by a transition rather than a level. Manchester coding states that there will always be a transition of the message signal at the mid-point of the data bit frame. What occurs at the bit edges depends on the state of the previous bit frame and does not always produce a transition. A logical 1 is defined as a mid-point transition from low to high and a 0 is a mid-point transition from high to low.[1] An example of a Manchester encoding is shown below in Fig 4.

Figure 4: Manchester Encoding.

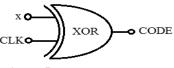

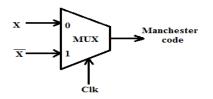

The Manchester encoding can be implemented using an XOR gate where the clock signal and the data signal are XORed together to obtain the encoded data as shown in the diagram below (Fig 5.)

Figure 5: Manchester encoder

#### **3.3 SOLS Technique**

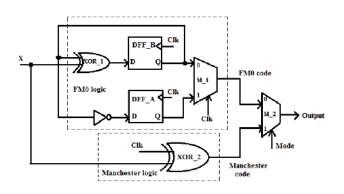

Normally DSRC encoders make use of both the FM0 and the Manchester encoding. Hence both the encoders can be combined together to form a reusable encoder. Such a reusable encoder can be illustrated as shown in the figure 6.

Figure 6: Reusable encoder

This block diagram can be further simplified using the SOLS technique. The SOLS encoder consists of mainly two methods, area compact retiming and the balance logic simplification. [1]

#### 3.3.1Area Compact Retiming

This method is mainly used in simplifying the FM0 encoder. For FM0 encoder, the state code of each state A(t) and B(t) is stored into separate flip flops. Since the transition of state code only depends on B(t), the encoder needs only a single

bit flip flop. Hence the block diagram is rearranged as shown in the diagram 7.

Figure 7: Simplified FM0 encoder

#### 3.3.2Balance Logic Simplification

This technique deals with the Manchester encoder. Usually Manchester encoding can be treated as the XORing between the input signal and the clock. But it can also be treated as a Multiplexer where the clock is given as the select input and the data and its complement is given as the data input. This is better explained by the diagram 8.

Figure 8: Simplified Manchester encoder

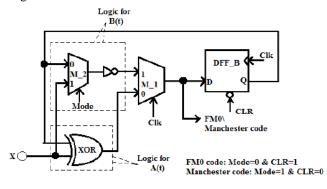

The above specified simplified encoders are combined together to form the SOLS encoder. This is shown in the diagram 9.

Figure 9: SOLS encoder

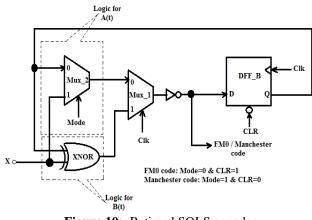

The disadvantage of this SOLS encoder is that there is an unbalance in the computation time which results in glitch. Inorder to avoid that, the NOT gate is moved to the output part of the first Mux and the XOR gate is replaced by the XNOR gate as shown in the diagram 10.

Figure 10: Retimed SOLS encoder

#### 4. Results and Discussion

Normally in DSRC communication, the FM0 or Manchester encodings are used. Hence an FM0 as well as a Manchester encoder is designed. For the purpose of using both the encodings, a reusable encoder is designed. But there exists wide code diversity between the two encodings. Hence the encoders are redesigned using SOLS technique. According to the area recompact technique and the balance logic simplification, FM0 and Manchester encoders are designed. Finally a reusable encoder structure is designed using SOLS technique. In order to prove the advantages of the SOLS encoder, both the reusable encoders are compared.

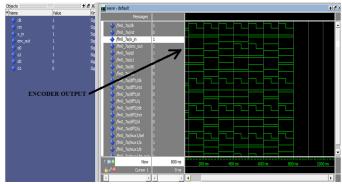

#### 4.1 FM0 Encoder

The simulated output of the FM0 encoder after simplification is shown in fig 11. The signal X in is treated as the input signal while the enc out is treated as the output signal. The reset (rst) signal is provided for resetting the whole system. Here we can see that the output signal encounters a transition for a logic 0 input and a transition after every clock signal. Also it is shown that, it does not encounter a transition for logic 1 input. This satisfies the conditions for FM0 encoding.

Figure 11: Simulated FM0 encoded output

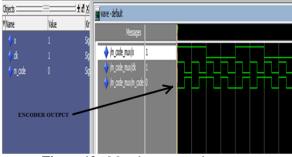

#### 4.2 Manchester encoder

A simple Manchester encoder is treated as an XOR gate. But after Balance Logic Simplification, the encoder is created by using a simple Mux. Here the clock pulse is given as the select input and the input data as well as it compliment is given as the input. The output simulated waveform is shown in fig 12. The output signal undergoes a logic low to logic high transition for a logic 0 input and a logic high to logic low transition for a logic 1 input. This satisfies the conditions for the Manchester encoding.

Figure 12: Manchester encoder output

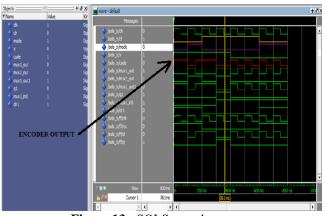

#### 4.3 SOLS Encoder

After combining the simplified FM0 and Manchester encoder, a reusable encoder for FM0 and Manchester encoding is obtained. The signal x and code are treated as both input and output signals respectively. Here the clear (clr) and the mode signal determine which encoding has to be followed. Whenever the clr = 0 and mode = 1; then FM0 encoding is followed. Also whenever the clr = 1 and the mode = 0; then Manchester encoding is followed as shown in the fig 13.

Figure 13: SOLS encoder output

## 4.4 Comparative study between a reusable and SOLS encoder

A comparative study between the encoders shows that the area consumption of SOLS encoder is low as compared to the other as shown in the table 1. The hardware utilization rate of the system determines the hardware efficiency of the system. Mathematically it can be represented by the ratio between the active components in a system to the total components. Experimentally it can be seen that the hardware utilization rate is much greater in the case of SOLS technique than for normal reusable system.

| Table 1: Comparative study |              |           |

|----------------------------|--------------|-----------|

| Parameters                 | Without SOLS | With SOLS |

| Number of slices           | 2            | 1         |

| Number of 4 input LUTs     | 3            | 2         |

| Number of IOs              | 5            | 5         |

| Number of bonded IOBs      | 5            | 5         |

| Total memory usage         | 179240 KB    | 178600 KB |

| Total delay                | 3.526ns      | 5.753ns   |

| Logic delay                | 89.9%        | 84.9%     |

| Route delay                | 10.1%        | 15.1%     |

| Levels of logic            | 1            | 3         |

From the comparison it is determined that the area consumption is much lesser in SOLS technique as compared to the other methods of designing a reusable system. Also the memory usage is reduced along with its logic delay. At the same time, the level of logic is improved.

## 5. Future Modification

DSRC communication offers an easy and reliable vehicular communication. In such a communication system, the encoding and decoding part can consume a large memory space as well as it can reduce device utilization. Hence a new SOLS decoder system can also be put forward along with the encoder part so as to reduce the memory wastage further.

## 6. Conclusion

The intelligent transport system has its own advantages like smooth traffic control, vehicular safety etc. To implement such a system, DSRC communication protocol is used. In DSRC communication, the safety messages are encoded and transmitted to the other DSRC equipped vehicles which in turn enhances the security of the vehicles. The data is encoded using FM0 and Manchester encoding. But the wide code diversity limits the hardware utilization rate of such a reusable encoder. Hence a new method of designing such an encoder called SOLS technique can be used. The SOLS encoder is of better advantage than the normal reusable encoder in terms of device utilization. Besides the logic delay and memory usage of the system also get reduced.

## References

- [1] Yu-Hsuan Lee, Cheng-Wei Pan ;Fully Reused VLSI Architecture of FM0/Manchester Encoding Using SOLS Technique for DSRC Applications IEEE trans. Very Large Scale Integr. (VLSI) Syst., vol. pp, issue 99, Feb 2014

- [2] Sarika. G. Joshi, Vaishali S Dhongde., HDLC Protocol Implementation Using VHDL, IJIRSET., vol. 3. Special issue 4, April 2014.

- [3] F. Ahmed-Zaid, F. Bai, S. Bai, C. Basnayake, B. Bellur, S. Brovold, et al., Vehicle safety communications Applications (VSC-A) final report, U.S. Dept. Trans., Nat. Highway Traffic Safety Admin., Washington, DC, USA, Rep. DOT HS 810 591, Sep. 2011.

- [4] J. B. Kenney, Dedicated short-range communications (DSRC) standards in the United States, Proc. IEEE, vol. 99, no. 7, pp. 11621182, Jul. 2011.

- [5] A. Karagounis, A. Polyzos, B. Kotsos, and N. Assimakis, A 90nm Manchester code generator with CMOS switches

## Volume 4 Issue 2, February 2015 www.ijsr.net

running at 2.4 GHz and 5 GHz, in Proc. 16th Int. Conf. Syst., Signals Image Process., Jun. 2009, pp. 14.

- [6] Y.-C. Hung, M.-M. Kuo, C.-K. Tung, and S.-H. Shieh, High-speed CMOS chip design for Manchester and Miller encoder, in Proc. Intell. Inf. Hiding Multimedia Signal Process., Sep. 2009, pp. 538541.

- [7] M. A. Khan, M. Sharma, and P. R. Brahmanandha, FSM based FM0 and Miller encoder for UHF RFID tag emulator, in Proc. IEEE Adv. Comput. Conf., Mar. 2009, pp. 13171322.

- [8] M. A. Khan, M. Sharma, and P. R. Brahmanandha, FSM based Manchester encoder for UHF RFID tag emulator, in Proc. Int. Conf. Comput., Commun. Netw., Dec. 2008, pp. 16.

- [9] J. Daniel, V. Taliwal, A. Meier, W. Holfelder, and R. Herrtwich, Design of 5.9 GHz DSRC-based vehicular safety communication, IEEE Wireless Commun. Mag., vol. 13, no. 5, pp. 3643, Oct. 2006.