## International Journal of Science and Research (IJSR) ISSN (Online): 2319-7064

Index Copernicus Value (2015): 78.96 | Impact Factor (2015): 6.391

# Implementation of Low Power Adiabatic based Inverter for Dynamic Comparator

## Heena Parveen<sup>1</sup>, Vishal Moyal<sup>2</sup>

<sup>1, 2</sup>Department of Electronics & Telecommunication Engineering, SSTC, SSITM, Bhilai, India

Abstract: The requirement for portable battery operating devices is escalating nowadays, hence low power methodologies are being favoured for high speed applications. Symmetric circuits with regenerative feedback provide opportunity to spot new structures that may be mainly helpful. Regenerative feedback is generally used in Dynamic Comparators and hardly ever in non clocked comparators. In the process of designing high speed ADCs (Analog-to-Digital Converters), Dynamic Comparator is generally used and can be simply designed. Dynamic comparators have a wide use in high speed ADCs because of their fast speed, high input impedance, full-swing output and low power consumption. To further reduce the power consumption, a novel Dynamic Comparator has been proposed where the back-to-back inverter of a conventional dynamic comparator is being replaced by the DFAL (Diode Free Adiabatic Logic) inverter that utilizes the adiabatic logic principle. For the corroboration of performance, the design is simulated by the Cadence Virtuoso Spectre simulator in gdpk 90nm Technology.

Keywords: Conventional Dynamic Comparator, CMOS inverter, Adiabatic Logic, DFAL inverter

#### 1. Introduction

The comparator is considered to be an important analog circuit that is required as a main part in Analog-to-Digital Converters (ADCs). Comparator basically compares one input voltage signal against another voltage signal and a binary output signal is generated as per the comparison. Dynamic Comparators which fall under the category of regenerative comparators have a wide use in high speed Analog-to-Digital Converters [1] owing to their lesser power dissipation, high speed and no static power consumption. Despite having such benefits, Dynamic Comparators suffer from certain device mismatches [2] such as parasitic node capacitance, threshold voltage and current factor  $\beta$  which are the prime reason for causing random offset voltages in comparators by deteriorating their performance. Employing offset cancellation or calibration techniques [3-5] while implementing comparator is also an effective methodology to alleviate this issue. Moreover, the reduction in the offset voltage can be done by means of a preamplifier in the design of comparator, but at the cost of more power consumption and complexity.

It is also observed that in conventional CMOS circuits, the power consumption is proportional to the square of the supply voltage and load capacitance [6], thus the researchers are focussing on supply voltage scaling and reducing the circuit capacitance so that the power consumption can be reduced. For supply voltage scaling, the threshold voltage  $(V_t)$  of transistor should be proportionally scaled down, though reducing the threshold voltage  $(V_t)$  of transistor result in a proportional increase in sub-threshold leakage current. The circuit capacitance could be further minimized by a reduction in the device sizes, but this will affect the driving capability of the circuit.

Because of these constraints, in current era, adiabatic logic systems have been used with the intention of reducing the

power consumption. Different adiabatic logic circuits have been proposed [7–14] based on the functioning of charge recovery principle. Adiabatic logic circuits [15] are considered as low power circuits which make use of reversible logic [16] for conservation of energy. Adiabatic logic is an attractive low power methodology which can be used as an alternative to standard CMOS circuits by providing means of reusing the energy that is stored in the load capacitor instead of following the usual means of discharging the load capacitance to the ground and wasting this energy.

### 2. CMOS Inverter

In the conventional CMOS circuits, the occurrence of power dissipation arises mainly during the device switching. During the voltage transition of the nodes, the power is dissipated while charging or discharging of the parasitic capacitances throughout the switching operation. A node capacitance C<sub>L</sub> is charged from 0 to  $V_{dd}$ , and an amount of energy =  $V_{dd}$ .Q  $(=C_LV_{dd}^{2})$  is drawn from the supply. During the phase when the charge is going up, one half of the energy, i.e. ½ C<sub>L</sub>V<sub>dd</sub><sup>2</sup> is dissipated as heat in conducting PMOS transistor, and the other half energy i.e.  $\frac{1}{2} C_L V_{dd}^2$  is stored in load capacitances. During the phase when the charge is going down, the energy that has stored in output load capacitance is dissipated in nMOS transistor. This switching energy dissipation could be minimized by a reduction in the physical capacitance and supply voltage. But there exists a drawback when the supply voltage V<sub>dd</sub> reduces, i.e. increase in the sub-threshold leakage current. Reduction in the circuit capacitances can be done by reducing the device sizes, however this will affect the driving capability and speed of the circuit.

### 3. DFAL Inverters

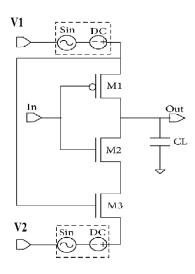

The circuit diagram of a DFAL inverter is shown in figure 1. These circuits have an attractive feature that they are free of diodes i.e. there are no diodes in their charging/discharging

Volume 6 Issue 1, January 2017

www.ijsr.net

<u>Licensed Under Creative Commons Attribution CC BY</u>

Index Copernicus Value (2015): 78.96 | Impact Factor (2015): 6.391

path. It consists of two split-level sinusoidal power clock supply  $V_1$  and  $V_2$  where one of the clocks will be in phase whereas the other one will be inverted. The voltage level of  $V_1$  exceeds  $V_2$  by  $V_1/2$  which will minimize the voltage difference between the electrodes and this will result in the reduction of power dissipation. Charging and discharging of the load capacitance by the split-level power clock is relatively slower than other adiabatic power clocks. As the efficiency of adiabatic circuits depends on how slow the load capacitance charges/discharges, the power dissipation can be further minimized.

Figure 1: DFAL Inverter

The resemblance of the static CMOS logic can be seen in the schematic of DFAL; however the circuit operation is in adiabatic mode. In the pull down network, the nMOS transistor (i.e. Transistor M<sub>3</sub>) which is adjacent to the transistor M2 is being used as a replacement of the diode for discharging. Power clock  $(V_1)$  controls the turning ON and turning OFF of this transistor (M<sub>3</sub>). In other adiabatic circuits, the main power dissipation which occurs at the diodes is because of the drop in threshold voltage (non adiabatic losses) at their discharging path while in DFAL circuits, it's because of the ON resistance (adiabatic losses) of the channel of transistor M<sub>3</sub>. The power dissipation owing to the ON resistance (of transistor M<sub>3</sub>) is considerably lower than the power that has been dissipated because of the drop in threshold voltage through the diodes. Moreover, this MOS transistor M<sub>3</sub> recycles charge from the output nodes and thus the further recovery of adiabatic losses can be done. But, still the power dissipation could not be removed totally and losses could not be fully recovered since the DFAL circuits are non reversible logic circuits. Therefore, the power dissipation is massively reduced in comparison to the adiabatic circuits (diode based) via the MOS transistor M3.

### 4. Dynamic Comparators

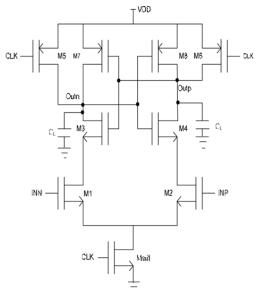

Dynamic Comparators are often described as Clocked comparators. Regenerative feedback is generally used in Dynamic Comparators and hardly ever in non clocked comparators. The conventional dynamic comparator which has a wide use in analog-to-digital converters is shown in

figure 2. Its operation is explained as follows: Dynamic Comparators have two operating modes: reset and evaluation phase. These operating modes operate as per the clock input that is provided to the circuit.

Figure 2: Conventional Dynamic Comparator

Figure 3: Schematic of Conventional Dynamic Comparator

When clock input is LOW in reset phase, transistor Mtail will be in OFF state. The reset transistors (M<sub>5</sub> and M<sub>6</sub>) will become ON and will pull both the output nodes (i.e. Out, and Out<sub>p</sub>) to voltage V<sub>dd</sub> for initiating the starting condition. During the evaluation phase, when the clock input becomes HIGH, transistors M<sub>5</sub> and M<sub>6</sub> will become OFF and simultaneously M<sub>tail</sub> will be ON due to which Out<sub>n</sub> and Out<sub>p</sub> which were at V<sub>dd</sub> will start falling with different rates of discharging. The case when  $V_{\mbox{\scriptsize INP}}$  is found to be greater than V<sub>INN</sub>, here the voltage at Out<sub>p</sub> will discharge faster than that of Out<sub>n</sub>. Since the voltage at the node Out<sub>p</sub> is discharged by the drain current of transistor M<sub>2</sub>, the voltage will fall down to V<sub>dd</sub>-|V<sub>thp</sub>| before the voltage at node Out<sub>n</sub> is discharged by the drain current of  $M_1$ , as a result of which transistor  $M_7$  will be ON. Consequently, the back-to-back inverters will begin the latch generation and the voltage at node Out<sub>n</sub> will become V<sub>dd</sub> and the voltage at node Out<sub>p</sub> will fall down to the ground. The case when  $V_{INN}$  is found to be greater than  $V_{INP}$ , the circuit will work in a vice versa manner.

Volume 6 Issue 1, January 2017

www.ijsr.net

<u>Licensed Under Creative Commons Attribution CC BY</u>

## 5. Proposed Dynamic Comparators

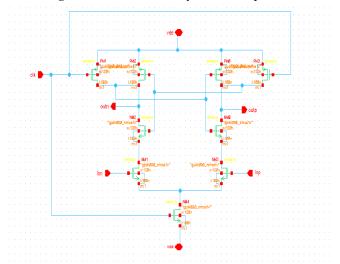

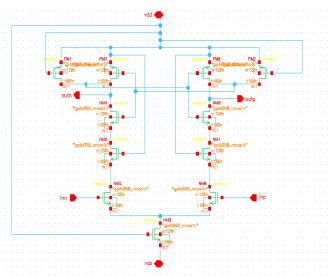

Figure 4 describes the schematic diagram of the proposed dynamic comparator. The main objective of the proposed comparator is to reduce the power consumption of the conventional dynamic comparator by a certain level, by replacing its back-to-back inverter with a DFAL inverter that shows lower power consumption than the CMOS inverter.

Figure 4: Schematic of Proposed Dynamic Comparator

#### 6. Simulation and Results

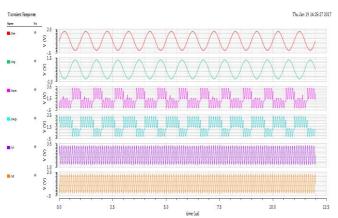

The Proposed Dynamic Comparator and Conventional dynamic comparator are designed and simulated by the Cadence Virtuoso Spectre simulator in gdpk 90nm Technology at a supply voltage of 3V. The Proposed Comparator as designed uses low power when compared against Conventional Dynamic Comparator.

**Figure 5:** Simulation output waveform of Proposed Dynamic Comparator using DFAL Inverter

## **6.1** Comparison of Proposed Dynamic Comparator with Conventional Dynamic Comparator

The performance of conventional and proposed dynamic comparator based on CMOS and DFAL inverters respectively has been calculated by varying the input frequency and load capacitances with respect to power and are shown in Tables 1 and 2 respectively. For analyzing frequency, load capacitance has been set to 1 fF and for analyzing load; power clock frequency and input have been set to 10 MHz and 1 MHz, respectively.

**Table 1:** Comparison of power at 1fF in 10 clock cycles of charging or discharging

| Frequency | Power Dissipation (µW) |                  | Power  |

|-----------|------------------------|------------------|--------|

|           | Conventional           | Proposed Dynamic | Saving |

|           | Dynamic Comparator     | Comparator       | (%)    |

| 1 MHz     | 23.88                  | 2.127            | 91.09  |

| 2.5 MHz   | 24.84                  | 3.164            | 87.26  |

| 5 MHz     | 25.23                  | 3.303            | 86.91  |

| 8 MHz     | 24.31                  | 4.202            | 82.71  |

**Table 2:** Comparison of power at 1MHz in 10 clock cycles of charging or discharging

| Load        | Power Dissipation (µW) |                  | Power  |

|-------------|------------------------|------------------|--------|

| Capacitance | Conventional           | Proposed Dynamic | Saving |

|             | Dynamic Comparator     | Comparator       | (%)    |

| 1f F        | 23.88                  | 2.127            | 91.09  |

| 5f F        | 23.89                  | 3.502            | 85.34  |

| 10f F       | 23.94                  | 5.958            | 75.11  |

| 15f F       | 23.99                  | 6.438            | 73.16  |

### 7. Conclusion

The results of simulation and evaluation of performance comparison show that the consumption of power in the proposed dynamic comparator is lower than the conventional dynamic comparator and provides 91.09 % of power saving at 1 MHz. The Proposed Dynamic Comparator would be very effective in high speed ADCs and other VLSI applications.

## References

- [1] V. Deepika and Sangeeta Singh, "Design and Implementation of a Low power, high speed comparator", Procedia Materials Science, Science Direct, 2015.

- [2] Jun He, Sanyi Zhan, Degang Chen, and R.L. Geiger, "Analyses of Static and Dynamic Random Offset Voltages in Dynamic Comparators," IEEE Trans. Circuits Syst. I: Reg. Papers, vol. 56, pp. 911-919, May 2009.

- [3] Islam T. Abougindia, Ismail Cevik, Fadi N. Zghoul, and Suat U.Ay, "A precision comparator design with a new foreground offset calibration technique", Analog Integrated Circuits and Signal Processing, Springer, May 2015, Volume 83, Issue 2, pp 243–255.

- [4] Takayuki Okazawa, Ippei Akita and Makoya Ishida, "A digitally calibrated dynamic comparator using timedomain offset detection", Analog Integrated Circuits and

Volume 6 Issue 1, January 2017

www.ijsr.net

Licensed Under Creative Commons Attribution CC BY

## International Journal of Science and Research (IJSR) ISSN (Online): 2319-7064

Index Copernicus Value (2015): 78.96 | Impact Factor (2015): 6.391

- Signal Processing, Springer, December 2014, Volume 81, Issue 3, pp 561–570.

- [5] M. Miyahara, Y. Asada, P. Daehwa and A. Matsuzawa, "A Low-Noise Self-Calibrating Dynamic Comparator for High-Speed ADCs", Proc. A-SSCC, IEEE Asian, pp.269-272, Nov. 2008.

- [6] N.H.E. Weste and D. Harris, CMOS VLSI Design: A Circuits and Systems Perspective, Addison-Wesley, Reading, Mass, USA, 3rdedition, 2004.

- [7] Minakshi Sanadhyaa and M.Vinoth Kumara, "Recent Development in Efficient Adiabatic Logic Circuits and Power Analysis with CMOS Logic", Procedia Computer Science, Science Direct, 3rd International Conference on Recent Trends in Computing 2015 (ICRTC-2015).

- [8] Irfan Ahmad Pindoo, Tejinder Singh, Amritpal Singh, Ankit Chaudhary and P. Mohan Kumar, "Power Dissipation Reduction Using Adiabatic Logic Techniques for CMOS Inverter Circuit", IEEE Conference Publications, 6th International Conference on Computing, Communication and Networking Technologies (ICCCNT), 2015.

- [9] Shipra Upadhyay, R. A. Mishra, R. K. Nagaria, and S. P. Singh, "DFAL: Diode-Free Adiabatic Logic Circuits". Hindawi Publishing Corporation ISRN Electronics Volume 2013, Article ID 673601, December 2012.

- [10] Pragati Upadhyay and Vishal Moyal (2016), "Implementation of Low Power Inverter using Adiabatic Logic", International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering, Vol. 5, Issue 6, June 2016.

- [11] Arun Kumar, Manoj Sharma, "Design and analysis of MUX using Adiabatic Techniques ECRL and PFAL", International Conference on Advances in computing, communication and informatics, IEEE, 2013.

- [12] Y. Moon and D. K. Jeong, "An efficient charge recovery logic circuit," IEEE Journal of Solid-State Circuits, vol. 31, no. 4, pp. 514–522,1996.

- [13] Yibin Ye, And Kaushik Roy, "QSERL: Quasi-static Energy Recovery Logic", IEEE Journal of Solid-state Circuits, vol.36. no.2, pp. 239-248, February 2001.

- [14] N. Anuar, Y. Takahashi, and T. Sekine, "Two phase clocked adiabatic static CMOS logic and its logic family," Journal of Semiconductor Technology and Science, vol. 10, no. 1, pp. 1–10, 2010.

- [15] P. Teichmann, "Fundamentals of Adiabatic Logic", Springer series in advance microelectronics, vol. 34, pp 5-22, 2012.

- [16] Prashant R. Yelekar and Sujata S. Chiwande, "Introduction to Reversible Logic Gates & its Application", Proceedings published in International Journal of Computer Applications® (IJCA), 2nd National Conference on Information and Communication Technology (NCICT), 2011.

Volume 6 Issue 1, January 2017 www.ijsr.net

Licensed Under Creative Commons Attribution CC BY